# MSP-FET430 Flash Emulation Tool (FET) (for Use With IAR Embedded Workbench Version 3+)

# **User's Guide**

Literature Number: SLAU138K June 2004-Revised May 2008

# **Contents**

| Prefa       | Ce                                                                                                                                                    | . 7 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1           | Get Started Now!                                                                                                                                      | . 9 |

| 1.1         | Flash Emulation Tool (FET) Overview                                                                                                                   | 10  |

| 1.2         | Kit Contents, MSP-FET430X110                                                                                                                          | 10  |

| 1.3         | Kit Contents, MSP-FET430PIF                                                                                                                           | 10  |

| 1.4         | Kit Contents, MSP-FET430Pxx0 ('P120, 'P140, 'P410, 'P430, 'P440)                                                                                      | 11  |

| 1.5         | Kit Contents, eZ430-F2013                                                                                                                             | 11  |

| 1.6         | Kit Contents, eZ430-T2012                                                                                                                             | 11  |

| 1.7         | Kit Contents, eZ430-F2500                                                                                                                             | 12  |

| 1.8         | Kit Contents, MSP-FET430UIF                                                                                                                           | 12  |

| 1.9         | Kit Contents, MSP-FET430Uxx ('U14, 'U28, 'U38, 'U23x0, 'U48, 'U64, 'U80, 'U100, 'U5x100)                                                              | 12  |

| 1.10        | Kit Contents, MSP-TS430xx ('PZ5x100)                                                                                                                  | 13  |

| 1.11        | Software Installation                                                                                                                                 |     |

| 1.12        | Hardware Installation, MSP-FET430X110                                                                                                                 | 14  |

| 1.13        | Hardware Installation, MSP-FET430PIF                                                                                                                  | 14  |

| 1.14        | Hardware Installation, MSP-FET430UIF                                                                                                                  | 14  |

| 1.15        | Hardware Installation, MSP-eZ430-F2013, MSP-eZ430-RF2500                                                                                              | 15  |

| 1.16        | Hardware Installation, MSP-FET430Uxx ('U14, 'U28, 'U38, 'U23x0, 'U48, 'U64, 'U80, 'U100, 'U5x100), MSP-FET430Pxx0 ('P120, 'P140, 'P410, 'P430, 'P440) | 15  |

| 1.17        | Flashing the LED                                                                                                                                      | 15  |

| 1.18        | Important MSP430 Documents on the CD-ROM and Web                                                                                                      | 15  |

| 2           | Development Flow                                                                                                                                      | 17  |

| 2.1         | Overview                                                                                                                                              | 18  |

| 2.2         | Using KickStart                                                                                                                                       | 18  |

|             | 2.2.1 Project Settings                                                                                                                                | 18  |

|             | 2.2.2 Creating a Project From Scratch                                                                                                                 | 20  |

|             | 2.2.3 Using an Existing IAR V1.x/V2.x/V3.x Project                                                                                                    | 21  |

|             | 2.2.4 Stack Management and .xcl Files                                                                                                                 | 21  |

|             | 2.2.5 How to Generate Texas Instruments .TXT (and Other Format) Files                                                                                 | 21  |

|             | 2.2.6 Overview of Example Programs                                                                                                                    | 21  |

| 2.3         | Using C-SPY                                                                                                                                           | 22  |

|             | 2.3.1 Breakpoint Types                                                                                                                                | 22  |

|             | 2.3.2 Using Breakpoints                                                                                                                               | 23  |

|             | 2.3.3 Using Single Step                                                                                                                               | 23  |

|             | 2.3.4 Using Watch Windows                                                                                                                             | 24  |

| 3           | Design Considerations for In-Circuit Programming                                                                                                      | 25  |

| 3.1         | Signal Connections for In-System Programming and Debugging, MSP-FET430PIF, MSP-FET430UIF, GANG430, PRGS430.                                           | 26  |

| 3.2         | External Power                                                                                                                                        | 20  |

| U. <u>—</u> | External Power                                                                                                                                        | 28  |

| 3.3         | Bootstrap Loader                                                                                                                                      |     |

| A.1  | Hardware                                                                 | 32                    |  |  |  |  |  |  |

|------|--------------------------------------------------------------------------|-----------------------|--|--|--|--|--|--|

| A.2  | Program Development (Assembler, C-Compiler, Linker)                      |                       |  |  |  |  |  |  |

| A.3  | Debugging (C-SPY)                                                        |                       |  |  |  |  |  |  |

| В    | Hardware                                                                 | 39                    |  |  |  |  |  |  |

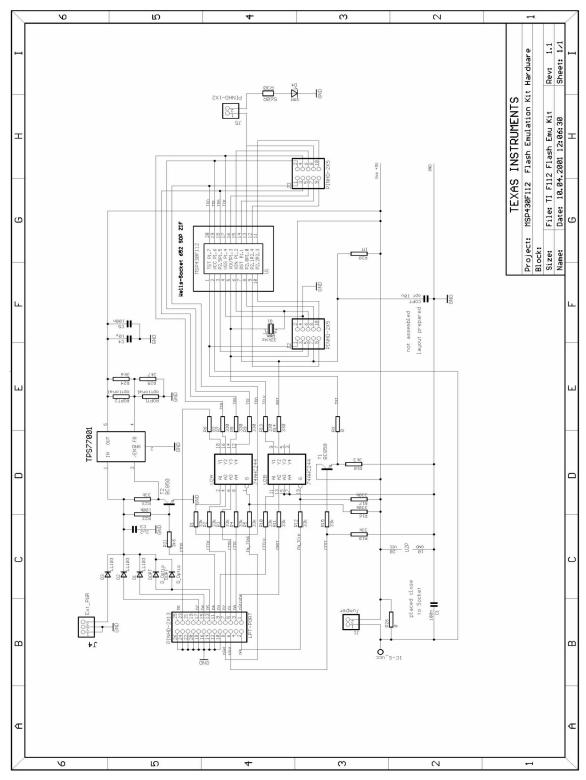

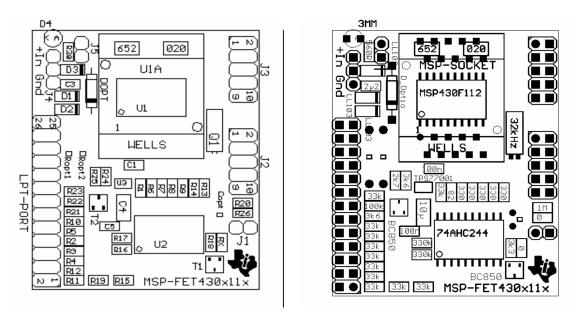

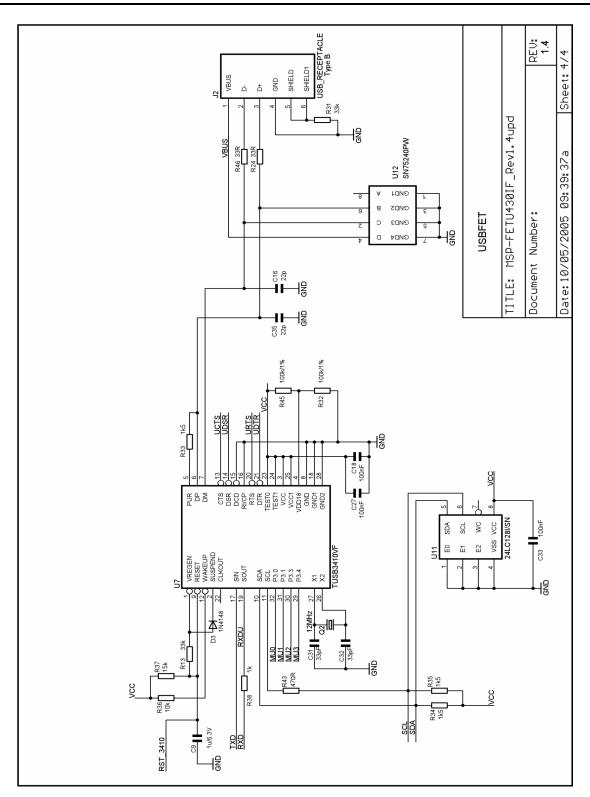

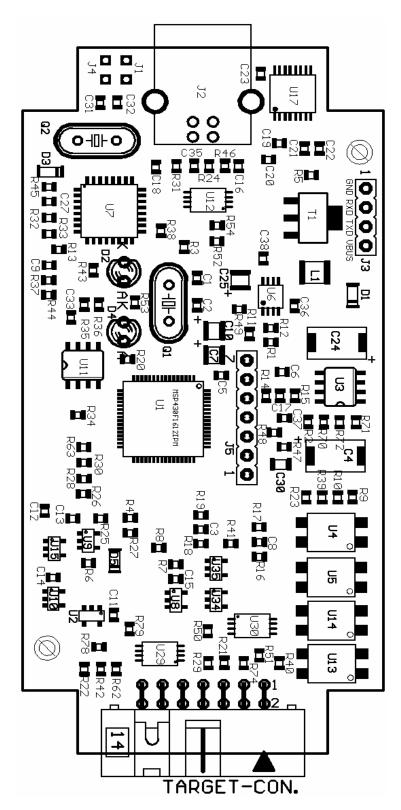

| B.1  | Schematics and PCBs                                                      | Schematics and PCBs40 |  |  |  |  |  |  |

| B.2  | MSP-FET430UIF Revision History                                           |                       |  |  |  |  |  |  |

| С    | FET-Specific Menus                                                       | <b>71</b>             |  |  |  |  |  |  |

| C.1  | Menus                                                                    | 72                    |  |  |  |  |  |  |

|      | C.1.1 Emulator → Device Information                                      | 72                    |  |  |  |  |  |  |

|      | C.1.2 Emulator → Release JTAG on Go                                      | 72                    |  |  |  |  |  |  |

|      | C.1.3 Emulator → Resynchronize JTAG                                      | 72                    |  |  |  |  |  |  |

|      | C.1.4 Emulator → Init New Device                                         | 72                    |  |  |  |  |  |  |

|      | C.1.5 Emulator → Secure - Blow JTAG Fuse                                 | 72                    |  |  |  |  |  |  |

|      | C.1.6 Emulator → Breakpoint Usage                                        | 72                    |  |  |  |  |  |  |

|      | C.1.7 Emulator $\rightarrow$ Advanced $\rightarrow$ Clock Control        | 72                    |  |  |  |  |  |  |

|      | C.1.8 Emulator $\rightarrow$ Advanced $\rightarrow$ Emulation Mode       | 72                    |  |  |  |  |  |  |

|      | C.1.9 Emulator $\rightarrow$ Advanced $\rightarrow$ Memory Dump          | 73                    |  |  |  |  |  |  |

|      | C.1.10 Emulator $\rightarrow$ Advanced $\rightarrow$ Breakpoint Combiner | 73                    |  |  |  |  |  |  |

|      | C.1.11 Emulator → State Storage Control                                  | 73                    |  |  |  |  |  |  |

|      | C.1.12 Emulator → State Storage Window                                   | 73                    |  |  |  |  |  |  |

|      | C.1.13 Emulator → Sequencer Control                                      | 73                    |  |  |  |  |  |  |

|      | C.1.14 Emulator → "Power on" Reset                                       | 73                    |  |  |  |  |  |  |

|      | C.1.15 Emulator $\rightarrow$ GIE on/off                                 | 73                    |  |  |  |  |  |  |

|      | C.1.16 Emulator → Leave Target Running                                   | 73                    |  |  |  |  |  |  |

|      | C.1.17 Emulator → Force Single Stepping                                  | 73                    |  |  |  |  |  |  |

| D    | 80-Pin MSP430F44x and MSP430F43x Device Emulation                        | <b>75</b>             |  |  |  |  |  |  |

| D.1  | F4xx/80-Pin Signal Mapping                                               | <b>76</b>             |  |  |  |  |  |  |

| Ε    | Hardware Installation Guide                                              | <b>79</b>             |  |  |  |  |  |  |

| E.1  | Hardware Installation                                                    | 80                    |  |  |  |  |  |  |

| Docu | Oocument Revision History85                                              |                       |  |  |  |  |  |  |

| Imno | rtant Notices                                                            | 86                    |  |  |  |  |  |  |

# **List of Figures**

| 3-1  | Signal Connections for 4-Wire JTAG Communication        | 27         |

|------|---------------------------------------------------------|------------|

| 3-2  | Signal Connections for 2-Wire Spy-Bi-Wire Communication | 28         |

| B-1  | MSP-FET430X110, Schematic                               | 40         |

| B-2  | MSP-FET430X110, PCB                                     | 41         |

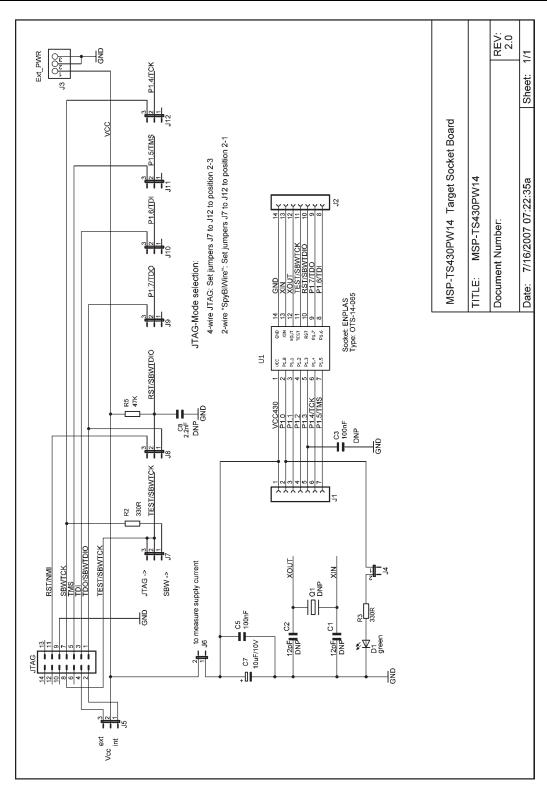

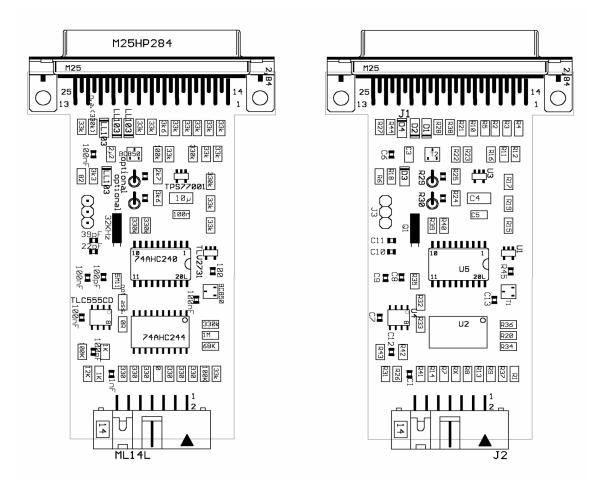

| B-3  | MSP-TS430PW14 Target Socket Module, Schematic           | 42         |

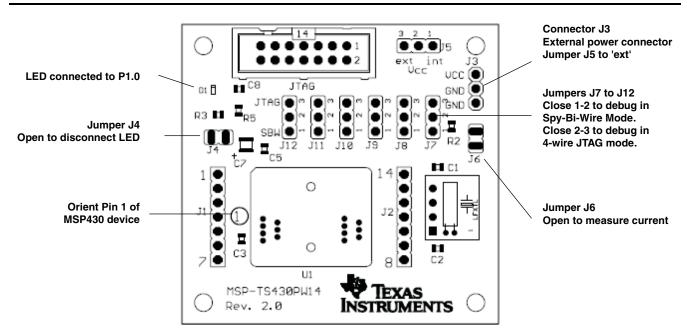

| B-4  | MSP-TS430PW14 Target Socket Module, PCB                 | 43         |

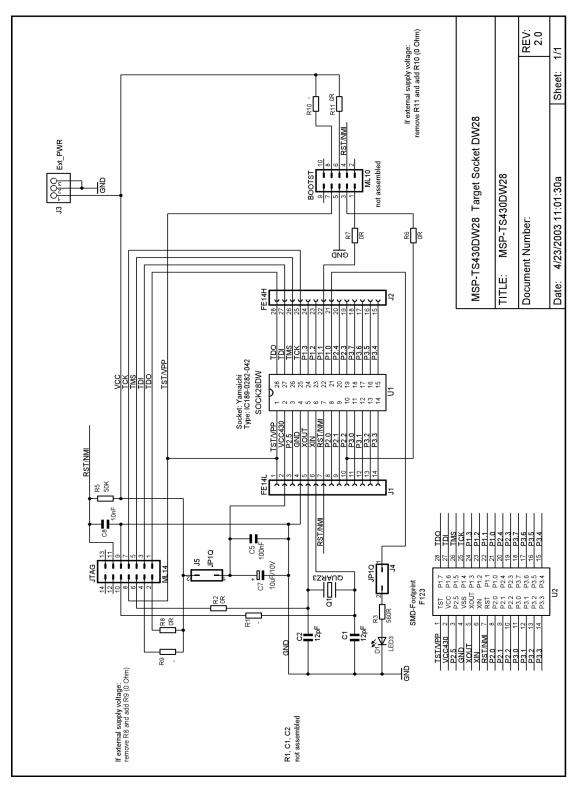

| B-5  | MSP-TS430DW28 Target Socket Module, Schematic           | 44         |

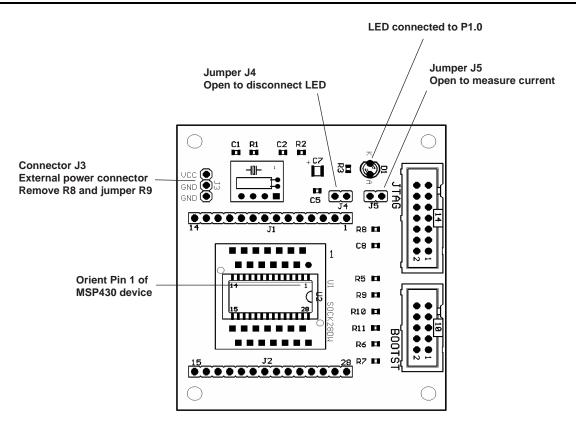

| B-6  | MSP-TS430DW28 Target Socket Module, PCB                 | 45         |

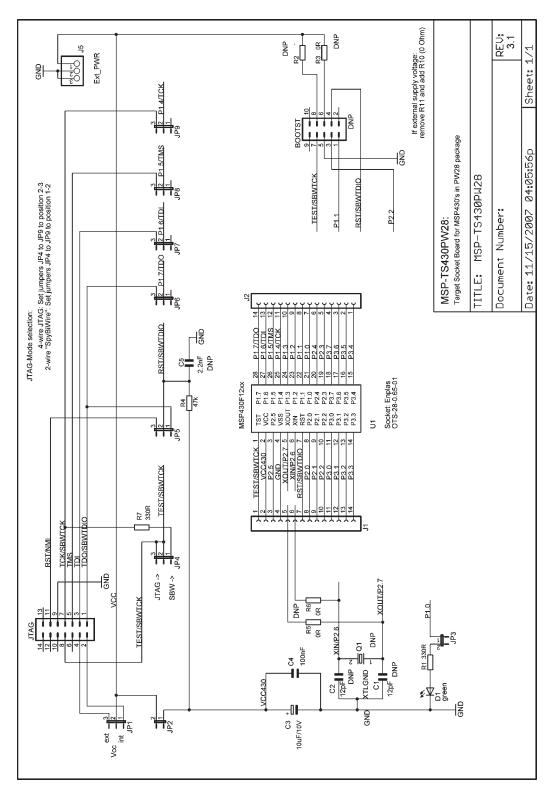

| B-7  | MSP-TS430PW28 Target Socket Module, Schematic           | 46         |

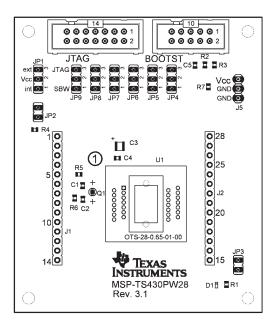

| B-8  | MSP-TS430PW28 Target Socket Module, PCB                 | 47         |

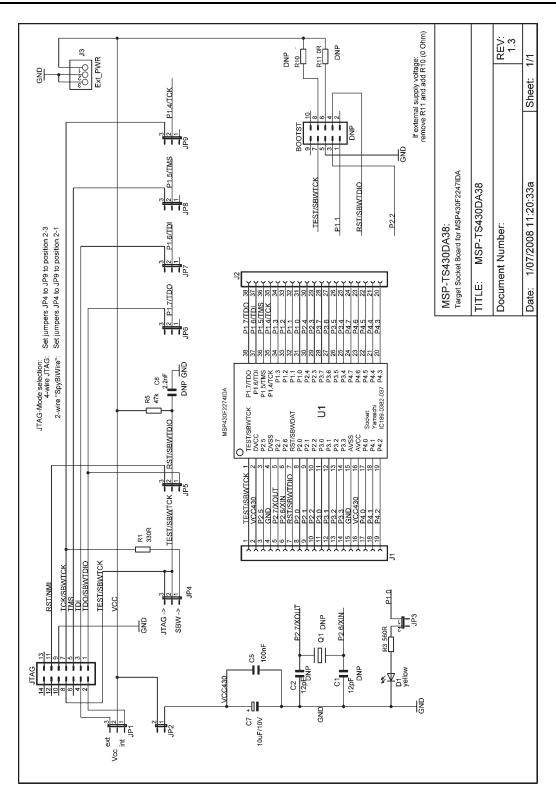

| B-9  | MSP-TS430DA38 Target Socket Module, Schematic           | 48         |

| B-10 | MSP-TS430DA38 Target Socket Module, PCB                 | 49         |

| B-11 | MSP-TS430QFN23x0 Target Socket Module, Schematic        | 50         |

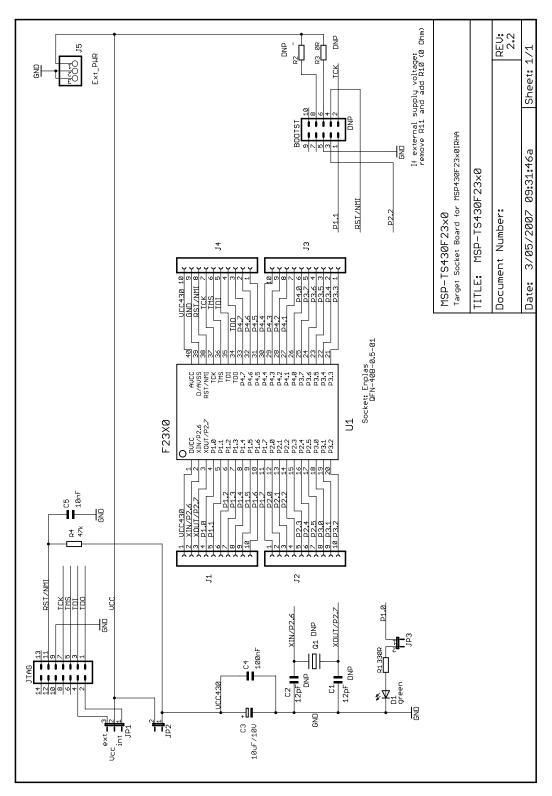

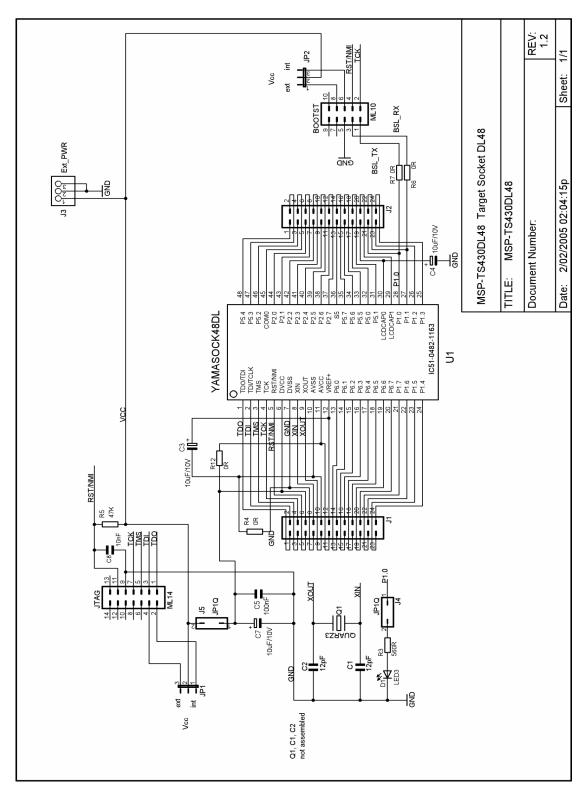

| B-12 | MSP-TS430QFN23x0 Target Socket Module, PCB              | 51         |

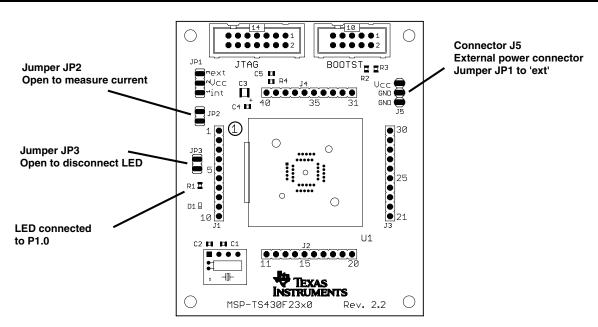

| B-13 | MSP-TS430DL48 Target Socket Module, Schematic           | 52         |

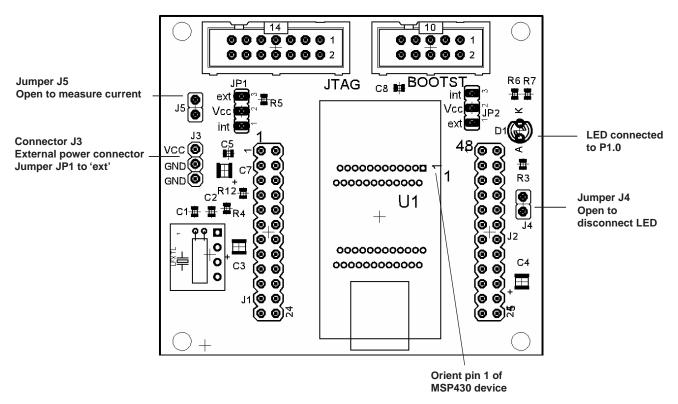

| B-14 | MSP-TS430DL48 Target Socket Module, PCB                 | 53         |

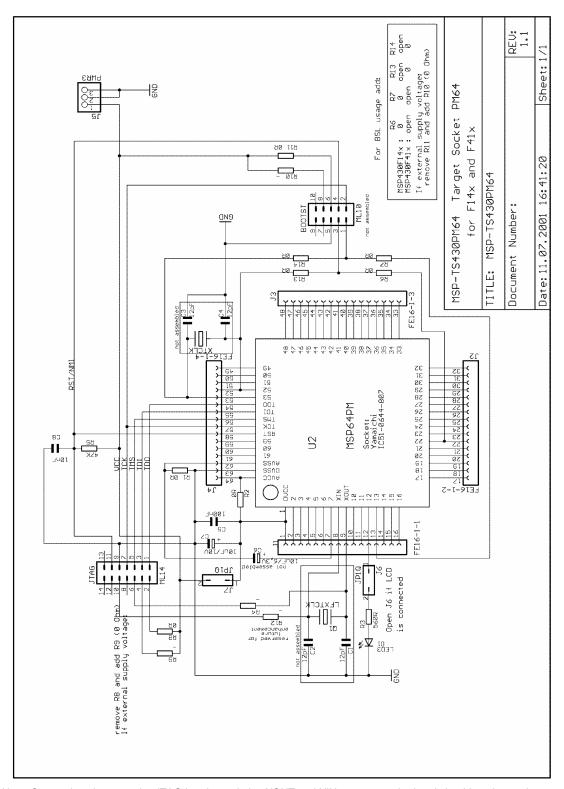

| B-15 | MSP-TS430PM64 Target Socket Module, Schematic           | 54         |

| B-16 | MSP-TS430PM64 Target Socket Module, PCB                 | 55         |

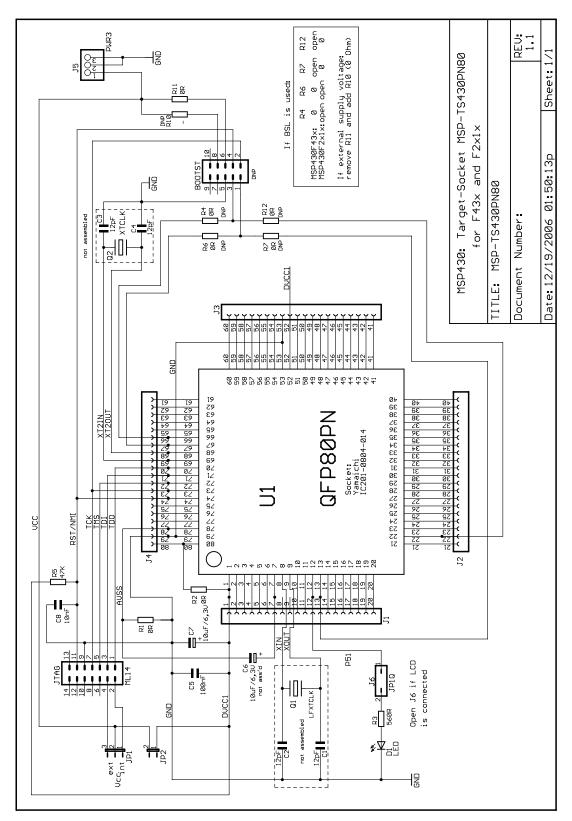

| B-17 | MSP-TS430PN80 Target Socket Module, Schematic           | 56         |

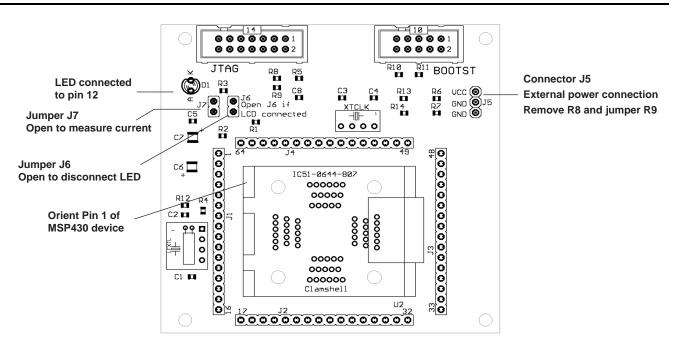

| B-18 | MSP-TS430PN80 Target Socket Module, PCB                 | 57         |

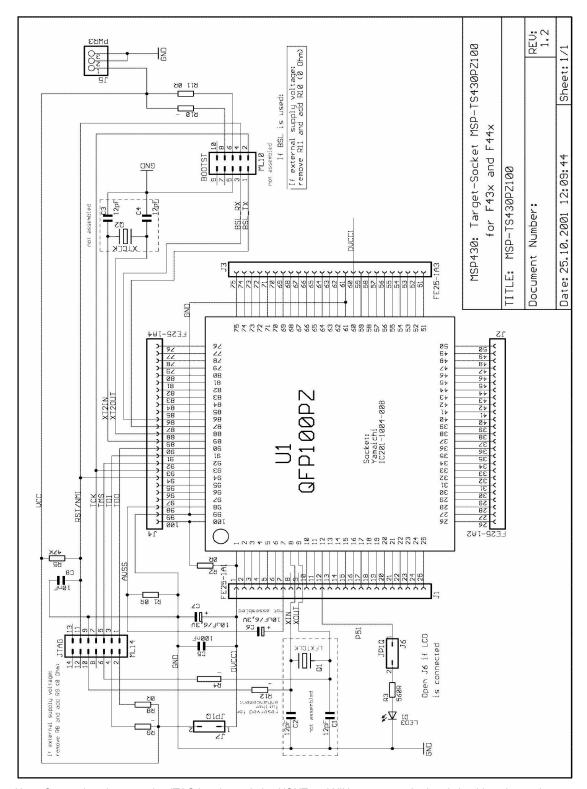

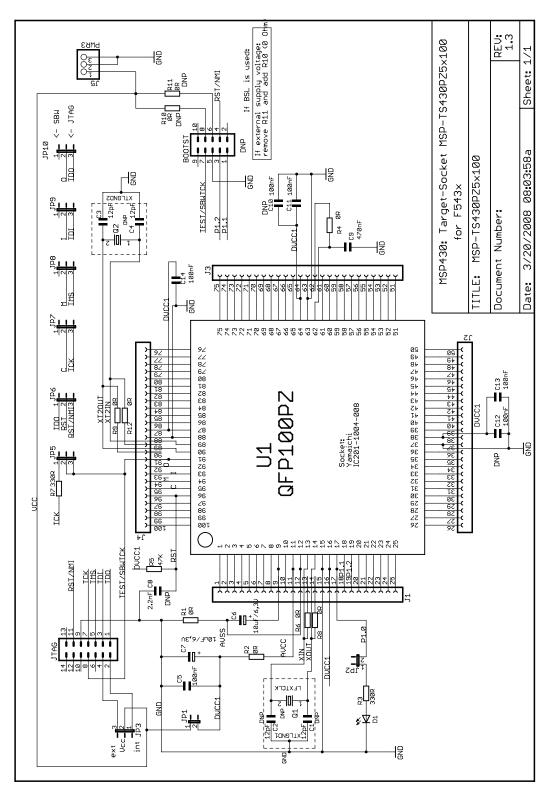

| B-19 | MSP-TS430PZ100 Target Socket Module, Schematic          | 58         |

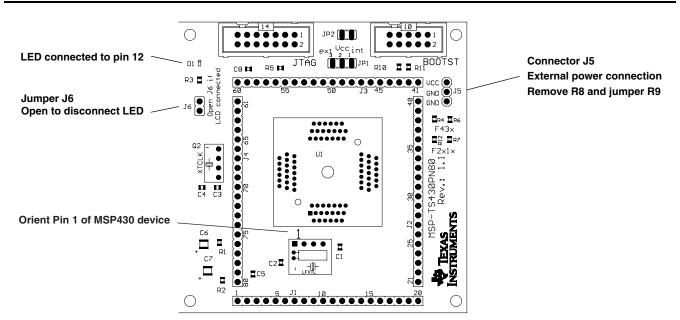

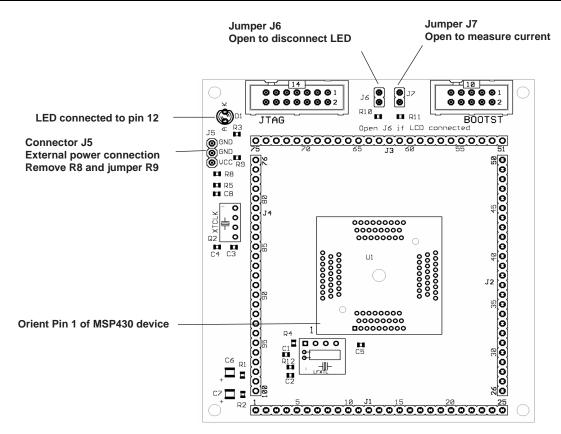

| B-20 | MSP-TS430PZ100 Target Socket Module, PCB                | <b>5</b> 9 |

| B-21 | MSP-TS430PZ5x100 Target Socket Module, Schematic        | 60         |

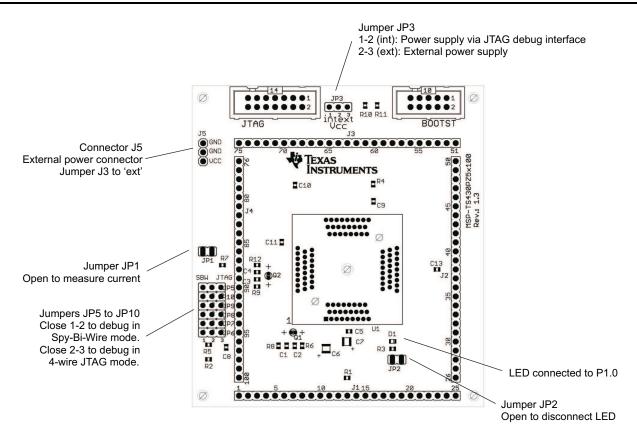

| B-22 | MSP-TS430PZ5x100 Target Socket Module, PCB              | 61         |

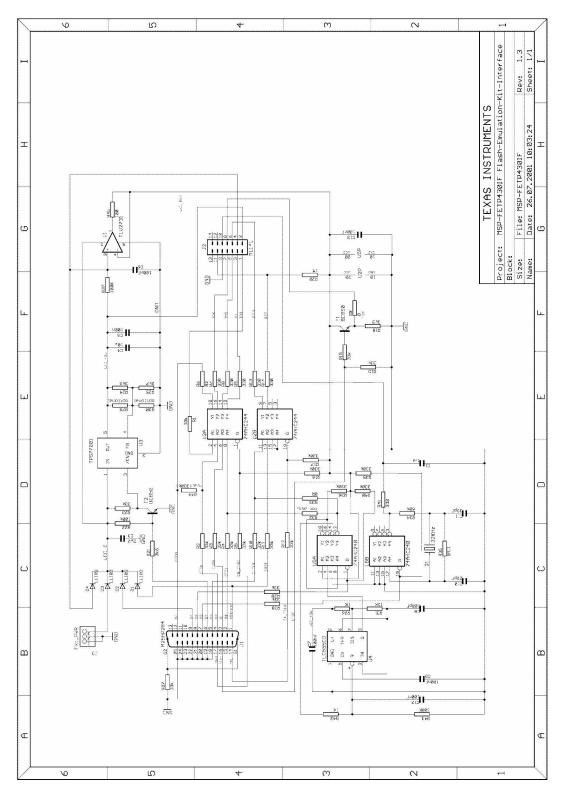

| B-23 | MSP-FET430PIF FET Interface Module, Schematic           | 62         |

| B-24 | MSP-FET430PIF FET Interface Module, PCB                 | 63         |

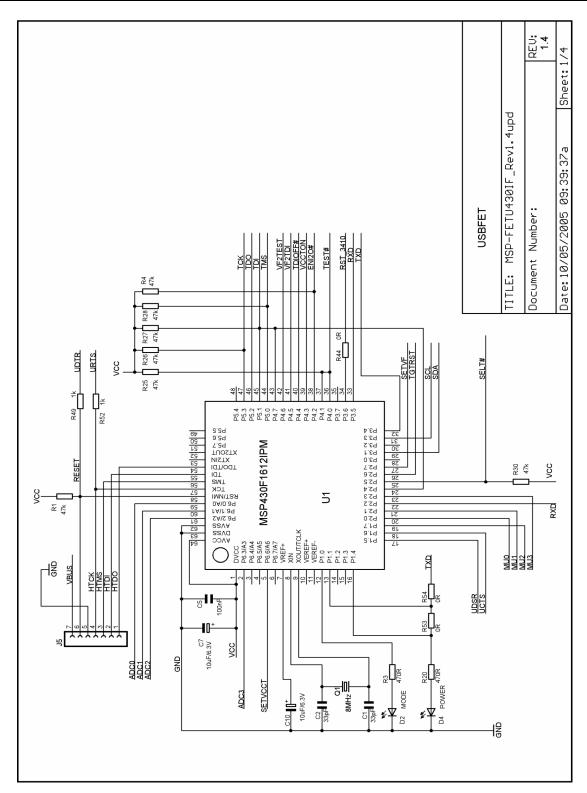

| B-25 | MSP-FET430UIF USB Interface, Schematic (1 of 4)         | 64         |

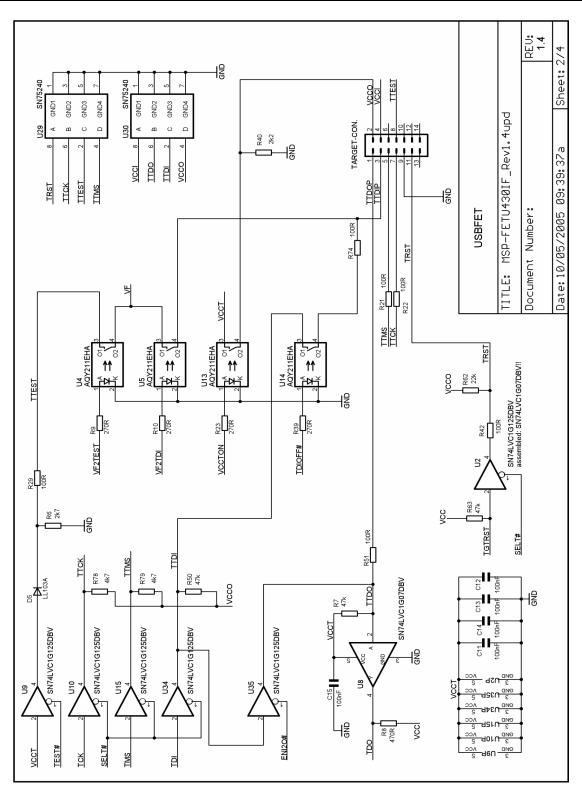

| B-26 | MSP-FET430UIF USB Interface, Schematic (2 of 4)         | 65         |

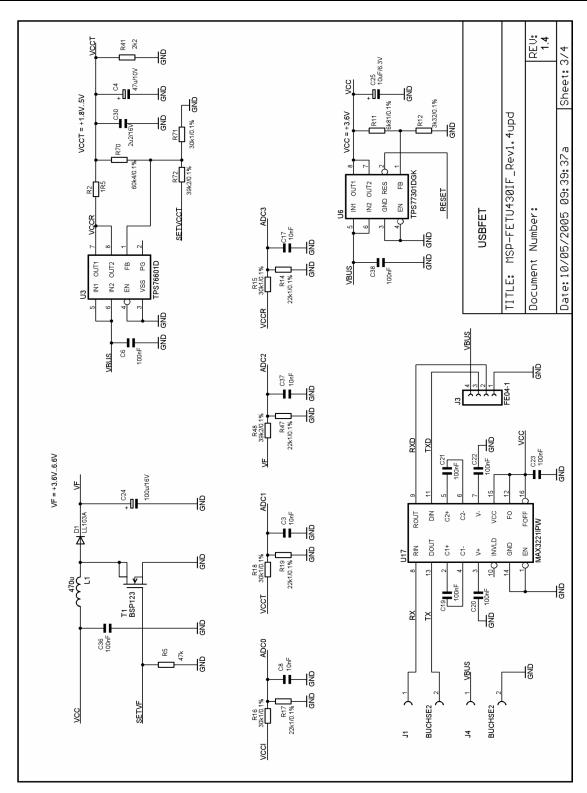

| B-27 | MSP-FET430UIF USB Interface, Schematic (3 of 4)         | 66         |

| B-28 | MSP-FET430UIF USB Interface, Schematic (4 of 4)         | 67         |

| B-29 | MSP-FET430UIF USB Interface, PCB                        | 68         |

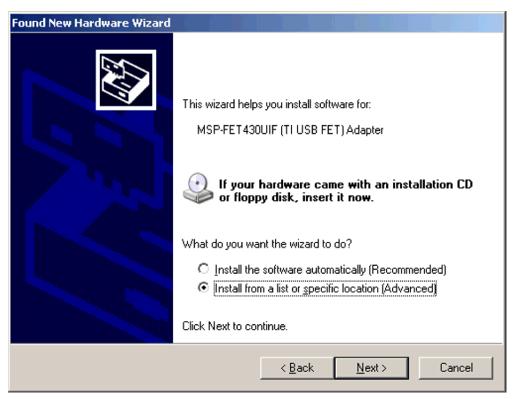

| E-1  | WinXP Hardware Recognition                              | 80         |

| E-2  | WinXP Hardware Wizard                                   | 80         |

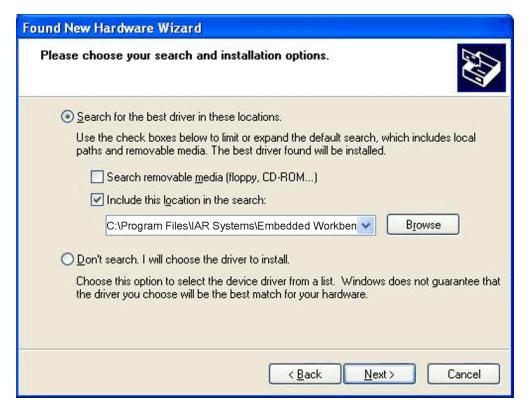

| E-3  | WinXP Driver Location Selection Folder                  | 81         |

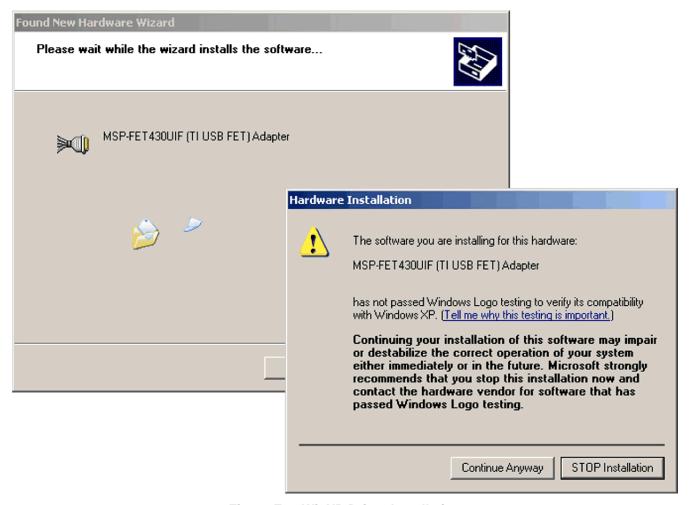

| E-4  | WinXP Driver Installation                               | 82         |

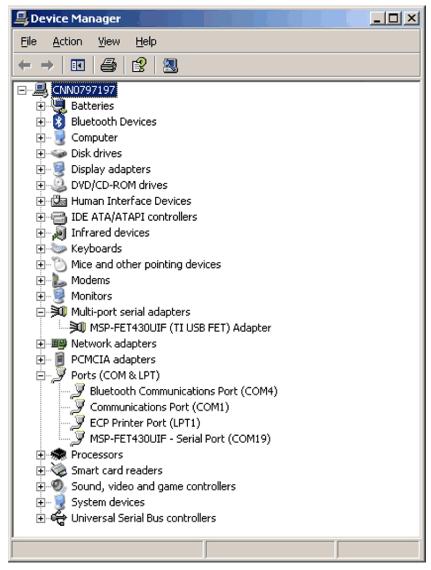

| E-5  | Device Manager Using MSP-FET430UIF or MSP-eZ430-F2013   |            |

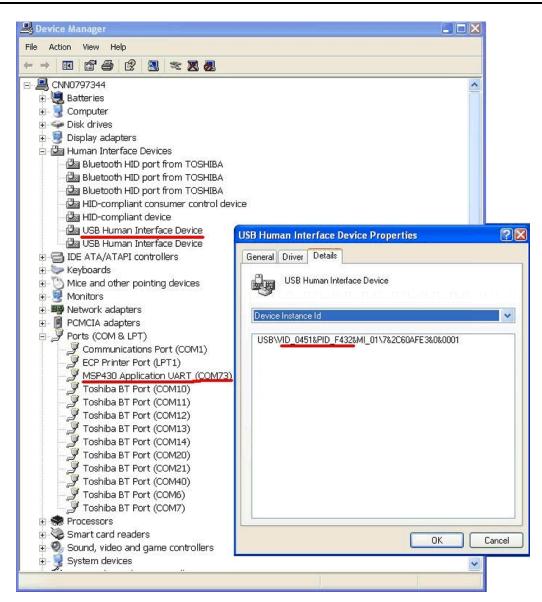

| E-6  | Device Manager Using MSP-eZ430-RF2500                   | 84         |

# **List of Tables**

| 1-1 | Flash Emulation Tool (FET) Features                       | 10 |

|-----|-----------------------------------------------------------|----|

| 2-1 | Number of Device Breakpoints and Other Emulation Features | 22 |

| D-1 | F4xx/80-pin Signal Mapping                                | 76 |

# Read This First

#### **About This Manual**

This manual documents the Texas Instruments MSP-FET430 Flash Emulation Tool (FET). The FET is the development tool for the MSP430 ultralow-power microcontroller. Both available interfaces, the parallel port interface and the USB interface, are described here.

### **How to Use This Manual**

Read and follow the instructions in Chapter 1, Get Started Now!. This chapter lists the expected contents of the FET, provides instructions on installing the hardware and software, and shows how to run the demonstration programs. After you see how quick and easy it is to use the FET, TI recommends that you read all of this manual.

This manual describes the setup and operation of the FET, but it does not fully describe the MSP430 or the development software systems. For details of these items, refer to the appropriate TI and IAR™ documents listed in Section 1.18, *Important MSP430 Documents on the CD-ROM and Web*.

This manual applies to the following tools (and devices):

- MSP-FET430PIF (debug interface with parallel port connection, for all MSP430 flash-based devices)

- MSP-FET430UIF (debug interface with USB connection, for all MSP430 flash-based devices)

- eZ430-F2013 (USB stick form factor interface with attached MSP430F2013 target, for all MSP430F20xx devices)

- eZ430-T2012 (three MSP430F2012-based target boards)

- eZ430-RF2500 (USB stick form factor interface with attached MSP430F2274/CC2500 target, for all MSP430F20xx and MSP430F22xx devices)

The following tools contain the parallel port debug interface (MSP-FET430PIF) and the respective target socket module:

- MSP-FET430X110 (for the MSP430F11xIDW, MSP430F11x1AIDW, and MSP430F11x2IDW devices)

- MSP-FET430P120 (for the MSP430F12xIDW and MSP430F12x2IDW devices)

- MSP-FET430P140 (for the MSP430F13xIPM, MSP430F14xIPM, MSP430F15xIPM, MSP430F16xIPM, and MSP430F161xIPM devices)

- MSP-FET430P410 (for the MSP430F41xIPM devices)

- MSP-FET430P430 (for the MSP430F43xIPN devices)

- MSP-FET430P440 (for the MSP430F43xIPZ and MSP430F44xIPZ devices)

The following tools contain the USB debug interface (MSP-FET430UIF) and the respective target-socket module:

- MSP-FET430U14 (for MSP430 devices in 14-pin PW packages)

- MSP-FET430U28 (for MSP430 devices in 20- and 28-in DW or PW packages)

- MSP-FET430U38 (for MSP430 devices in 38-pin DA packages)

- MSP-FET430U23x0 (for MSP430F2330/F2350/F2370 devices in 40-pin RHA packages only)

- MSP-FET430U48 (for MSP430 devices in 48-pin DL package)

- MSP-FET430U64 (for MSP430 devices in 64-pin PM package)

- MSP-FET430U80 (for MSP430 devices in 80-pin PN package)

- MSP-FET430U100 (for MSP430 devices in 100-pin PZ package)

- MSP-FET430U5x100 (for MSP430F5x devices in 100-pin PZ package)

All trademarks are the property of their respective owners.

Stand-alone target-socket modules (without debug interface):

MSP-TS430PZ5x100 (for MSP430F5x devices in 100-pin PZ packages)

These tools contain the most up-to-date materials available at the time of packaging. For the latest materials (data sheets, user's guides, software, application information, etc.), visit the TI MSP430 web site at <a href="https://www.ti.com/msp430">www.ti.com/msp430</a>, or contact your local TI sales office.

# **Information About Cautions and Warnings**

This book may contain cautions and warnings.

#### **CAUTION**

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

# **WARNING**

This is an example of a warning statement.

A warning statement describes a situation that could potentially cause harm to you.

The information in a caution or a warning is provided for your protection. Read each caution and warning carefully.

#### **Related Documentation From Texas Instruments**

MSP430xxxx device data sheets

MSP430x1xx Family User's Guide, SLAU049

MSP430x2xx Family User's Guide, SLAU144

MSP430x3xx Family User's Guide, SLAU012

MSP430x4xx Family User's Guide, SLAU056

MSP430x5xx Family User's Guide, SLAU208

#### If You Need Assistance

Support for the MSP430 device and the FET is provided by the Texas Instruments Product Information Center (PIC). Contact information for the PIC can be found on the TI web site at <a href="www.ti.com">www.ti.com</a>. Additional device-specific information can be found on the MSP430 web site at <a href="www.ti.com/msp430">www.ti.com/msp430</a>.

#### Note: KickStart™ is supported by Texas Instruments.

Although KickStart is a product of IAR, Texas Instruments provides the support for it. Therefore, please do not request support for KickStart from IAR. Please consult the extensive documentation provided with KickStart before requesting assistance.

# **FCC Warning**

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio-frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio-frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user, at his own expense, will be required to take whatever measures may be required to correct this interference.

# Get Started Now!

This chapter lists the contents of the FET, provides instruction on installing the software and hardware, and shows how to run the demonstration programs.

Topic **Page** Flash Emulation Tool (FET) Overview......10 1.1 1.2 Kit Contents, MSP-FET430X110 ...... 10 1.3 1.4 Kit Contents, MSP-FET430Pxx0 ('P120, 'P140, 'P410, 'P430, 'P440).. 11 1.5 Kit Contents, eZ430-F2013 ...... 11 1.6 Kit Contents, eZ430-T2012 ...... 11 1.7 Kit Contents, eZ430-F2500 ...... 12 Kit Contents, MSP-FET430UIF ...... 12 1.8 Kit Contents, MSP-FET430Uxx ('U14, 'U28, 'U38, 'U23x0. 'U48. 1.9 'U64, 'U80, 'U100, 'U5x100) ...... 12 1.10 Software Installation...... 14 1.11 Hardware Installation, MSP-FET430X110......14 1.13 1.14 Hardware Installation, MSP-FET430UIF ...... 14 Hardware Installation, MSP-eZ430-F2013, MSP-eZ430-RF2500 ...... 15 1.15 Hardware Installation, MSP-FET430Uxx ('U14, 'U28, 'U38, 'U23x0, 'U48, 'U64, 'U80, 'U100, 'U5x100), MSP-FET430Pxx0 ('P120, 'P140, 1.17 1.18

# 1.1 Flash Emulation Tool (FET) Overview

TI offers several flash emulation tools according to different requirements.

Table 1-1. Flash Emulation Tool (FET) Features

|                                                                  | eZ430-F2013 | eZ430-RF2500 | MSP-FET430UIF | MSP-FET430PIF |

|------------------------------------------------------------------|-------------|--------------|---------------|---------------|

| Supports all MSP430 flash-based devices (F1xx, F2xx, F4xx, F5xx) |             |              | Х             | Х             |

| Supports MSP430F20xx devices only                                | Х           |              |               |               |

| Supports MSP430F20xx/F21x2/F22xx only                            |             | Х            |               |               |

| Allows fuse blow                                                 |             |              | Х             |               |

| Adjustable target supply voltage                                 |             |              | Х             |               |

| Fixed 2.8-V target supply voltage                                |             |              |               | Х             |

| Fixed 3.6-V target supply voltage                                | Х           | Х            |               |               |

| 4-wire JTAG                                                      |             |              | X             | Х             |

| 2-wire JTAG <sup>(1)</sup>                                       | Х           | Х            | Х             |               |

| Application UART                                                 |             | Х            |               |               |

| Supported by CCE                                                 | X           | Х            | Х             | Х             |

| Supported by IAR                                                 | Х           | Х            | Х             | Х             |

<sup>(1)</sup> The 2-wire JTAG debug interface is also referred to as Spy-Bi-Wire (SBW) interface.

# 1.2 Kit Contents, MSP-FET430X110

- One READ ME FIRST document

- One MSP430 CD-ROM

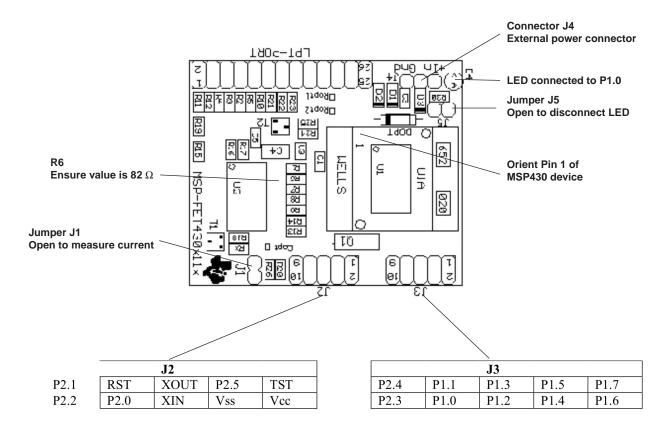

- One MSP-FET430X110 Flash Emulation Tool. This is the PCB on which is mounted a 20-pin ZIF socket for the MSP430F11xIDW, MSP430F11x1AIDW, or MSP430F11x2IDW device. A 25-conductor cable originates from the FET for connecting to the PC parallel port.

- One small box containing two MSP430F1121AIDW device samples

# 1.3 Kit Contents, MSP-FET430PIF

- One READ ME FIRST document

- One MSP430 CD-ROM

- One MSP-FET430PIF interface module

- One 25-conductor cable

- One 14-conductor cable

# 1.4 Kit Contents, MSP-FET430Pxx0 ('P120, 'P140, 'P410, 'P430, 'P440)

- One READ ME FIRST document

- One MSP430 CD-ROM

- One MSP-FET430PIF FET Interface module. This is the unit that has a 25-pin male D-Sub connector on one end of the case, and a 2×7-pin male connector on the other end of the case.

- One target socket module

**MSP-FET430P120:** One MSP-TS430DW28 target socket module. This is the PCB on which is mounted a 28-pin ZIF socket for the MSP430F12xIDW or MSP43012x2IDW device. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430P140:** One MSP-TS430PM64 target socket module. This is the PCB on which is mounted a 64-pin clam-shell-style socket for the MSP430F13xIPM, MSP430F14xIPM, MSP430F15xIPM, MSP430F16xIPM, or MSP430F161xIPM device. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430P410:** One MSP-TS430PM64 target socket module. This is the PCB on which is mounted a 64-pin clam-shell-style socket for the MSP430F41xIPM device. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430P430:** One MSP-TS430PN80 target socket module. This is the PCB on which is mounted an 80-pin ZIF socket for the MSP430F43xIPN device. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430P440:** One MSP-TS430PZ100 target socket module. This is the PCB on which is mounted a 100-pin ZIF socket for the MSP430F43xIPZ or MSP430F44xIPZ device. A 2×7-pin male connector is also present on the PCB.

- One 25-conductor cable

- One 14-conductor cable

- Four or eight headers

MSP-FET430P120: Four PCB 1×14-pin headers (two male and two female)

MSP-FET430P140: Eight PCB 1×16-pin headers (four male and four female)

MSP-FET430P410: Eight PCB 1×16-pin headers (four male and four female)

MSP-FET430P430: Eight PCB 1×20-pin headers (four male and four female)

MSP-FET430P440: Eight PCB 1×25-pin headers (four male and four female)

One small box containing two or four MSP430 device samples

**MSP-FET430P120:** MSP430F123IDW and/or MSP430F1232IDW **MSP-FET430P140:** MSP430F149IPM and/or MSP430F169IPM

MSP-FET430P410: MSP430F413IPM

MSP-FET430P430: MSP430F437IPN and/or MSP430FG439

MSP-FET430P440: MSP430F449IPZ

Consult the device data sheets for device specifications. Device errata can be found in the respective device product folder on the web provided as a PDF document. Depending on the device, errata may also be found in the device bug database at <a href="https://www.ti.com/sc/cgi-bin/buglist.cgi">www.ti.com/sc/cgi-bin/buglist.cgi</a>.

# 1.5 Kit Contents, eZ430-F2013

- One QUICK START GUIDE document

- One eZ430-F2013 CD-ROM

- One eZ430-F2013 development tool including one MSP430F2013 target board

#### 1.6 Kit Contents, eZ430-T2012

Three MSP430F2012-based target boards

#### 1.7 Kit Contents, eZ430-F2500

- One QUICK START GUIDE document

- One eZ430-RF2500 CD-ROM

- One eZ430-RF2500 development tool including one MSP430F2274/CC2500 target board

- One eZ430-RF2500T target board with battery holder and batteries

# 1.8 Kit Contents, MSP-FET430UIF

- One READ ME FIRST document

- One MSP430 CD-ROM

- One MSP-FET430UIF interface module

- One USB cable

- One 14-conductor cable

# 1.9 Kit Contents, MSP-FET430Uxx ('U14, 'U28, 'U38, 'U23x0, 'U48, 'U64, 'U80, 'U100, 'U5x100)

- One READ ME FIRST document

- One MSP430 CD-ROM

- One MSP-FETP430UIF USB interface module. This is the unit that has a USB B-connector on one end of the case, and a 2×7-pin male connector on the other end of the case.

- One target socket module

- One 32.768-kHz crystal

**MSP-FET430U14:** One MSP-TS430PW14 target socket module. This is the PCB on which is mounted a 14-pin ZIF socket. It fits all MSP430 devices in 14-pin PW packages. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U28:** One MSP-TS430DW28 or MSP-TS430PW28 target socket module. This is the PCB on which is mounted a 28-pin ZIF socket. It fits all MSP430 devices in 20- and 28-pin DW and PW packages. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U38:** One MSP-TS430DA38 target socket module. This is the PCB on which is mounted a 38-pin ZIF socket. It fits all MSP430 devices in 38-pin DA packages. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U23x0**: One MSP-TS430QFN23x0 (former name MSP-TS430QFN40) target socket module. This is the PCB on which is mounted a 40-pin ZIF socket. It fits only MSP430F2330/F2350/F2370 devices in 40-pin RHA package. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U48:** One MSP-TS430DL48 target socket module. This is the PCB on which is mounted a 48-pin ZIF socket. It fits all MSP430 devices in 48-pin DL package. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U64:** One MSP-TS430PM64 target socket module. This is the PCB on which is mounted a 64-pin ZIF socket. It fits all MSP430 devices in 64-pin PM package. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U80:** One MSP-TS430PN80 target socket module. This is the PCB on which is mounted a 80-pin ZIF socket. It fits all MSP430 devices in 80-pin PN package. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U100:** One MSP-TS430PZ100 target socket module. This is the PCB on which is mounted a 100-pin ZIF socket. It fits all MSP430 devices in 100-pin PZ package. A 2×7-pin male connector is also present on the PCB.

**MSP-FET430U5x100:** One MSP-TS430PZ5x100 target socket module. This is the PCB on which is mounted a 100-pin ZIF socket. It fits all MSP430F5x devices in 100-pin PZ package. A 2×7-pin male connector is also present on the PCB.

- One USB cable

- One 14-conductor cable

Four or eight headers

MSP-FET430U14: Four PCB 1×7-pin headers (two male and two female)

MSP-FET430U28: Four PCB 1×14-pin headers (two male and two female)

MSP-FET430U38: Four PCB 1×19-pin headers (two male and two female)

MSP-FET430U23x0: Eight PCB 1×10-pin headers (four male and four female)

MSP-FET430U48: Four PCB 2×24-pin headers (two male and two female)

MSP-FET430U64: Eight PCB 1×16-pin headers (four male and four female)

MSP-FET430U80: Eight PCB 1×20-pin headers (four male and four female)

MSP-FET430U100: Eight PCB 1×25-pin headers (four male and four female)

MSP-FET430U5x100: Eight PCB 1×25-pin headers (four male and four female)

One small box containing two or four MSP430 device samples

MSP-FET430U14: MSP430F2013IPW

MSP-FET430U28: MSP430F123IDW and/or MSP430F1232IDW or MSP430F2132IPW

MSP-FET430U38: MSP430F2274IDA MSP-FET430U23x0: MSP430F2370IRHA MSP-FET430U48: MSP430F4270IDL

MSP-FET430U64: MSP430F417IPM and MSP430F169IPM

MSP-FET430U80: MSP430FG439IPN

MSP-FET430U100: MSP430F449IPZ and MSP430FG4619IPZ

MSP-FET430U5x100: MSP430F5438IPZ

Consult the device data sheets for device specifications. Device errata can be found in the respective device product folder on the web provided as a PDF document. Depending on the device, errata may also be found in the device bug database at <a href="https://www.ti.com/sc/cgi-bin/buglist.cgi">www.ti.com/sc/cgi-bin/buglist.cgi</a>.

# 1.10 Kit Contents, MSP-TS430xx ('PZ5x100)

- One READ ME FIRST document

- One MSP430 CD-ROM

- One target socket module

- One 32.768-kHz crystal

**MSP-TS430PZ5x100:** One MSP-TS430PZ5x100 target socket module. This is the PCB on which is mounted a 100-pin ZIF socket. It fits all MSP430F5x devices in 100-pin PZ package. A 2×7-pin male connector is also present on the PCB.

Four or eight headers

MSP-TS430PZ5x100: Eight PCB 1×25-pin headers (four male and four female)

One small box containing two MSP430 device samples

MSP-TS430PZ5x100: MSP430F5438IPZ

Consult the device data sheets for device specifications. Device errata can be found in the respective device product folder on the web provided as a PDF document. Depending on the device, errata may also be found in the device bug database at <a href="https://www.ti.com/sc/cgi-bin/buglist.cgi">www.ti.com/sc/cgi-bin/buglist.cgi</a>.

Software Installation www.ti.com

#### 1.11 Software Installation

Follow the instructions on the supplied READ ME FIRST document to install the IAR Embedded Workbench™ KickStart. Read the file <Installation Root>\Embedded Workbench x.x\430\doc\readme.htm from IAR for the latest information about the Workbench. The term KickStart refers to the function-limited version of Embedded Workbench (including C-SPY™ debugger). KickStart is supplied on the CD-ROM included with each FET, and the latest version is available from the MSP430 web site.

The documents mentioned in the previous paragraph (and this document) can be accessed using: Start  $\rightarrow$  Programs  $\rightarrow$  IAR Systems  $\rightarrow$  IAR Embedded Workbench KickStart for MSP430 V3.

KickStart is compatible with Windows® 98, Windows 2000, Windows ME, Windows NT 4.0, Windows XP, and Windows Vista. However, the USB FET interface works only with Windows 2000, Windows XP, and Windows Vista.

### 1.12 Hardware Installation, MSP-FET430X110

- 1. Connect the 25-conductor cable originating from the FET to the parallel port of your PC. The driver for accessing the PC parallel port is installed during IAR Embedded Workbench installation. Note that a restart is required after the IAR Embedded Workbench installation for the driver to become active.

- 2. Ensure that the MSP430F1121AIDW is securely seated in the socket and that its pin 1 (indicated with a circular indentation on the top surface) aligns with the "1" mark on the PCB.

- 3. Ensure that jumpers J1 (near the non-socketed IC on the FET) and J5 (near the LED) are in place. Schematics of the FET and its parts are presented in Appendix B.

#### 1.13 Hardware Installation, MSP-FET430PIF

- 1. Use the 25-conductor cable to connect the FET interface module to the parallel port of your PC. The necessary driver for accessing the PC parallel port is installed during IAR Embedded Workbench installation. Note that a restart is required after the IAR Embedded Workbench installation for the driver to become active.

- 2. Use the 14-conductor cable to connect the parallel port debug interface module to a target board, such as an MSP-TS430xxx target socket module.

# 1.14 Hardware Installation, MSP-FET430UIF

- 1. Use the USB cable to connect the USB FET interface module to a USB port of your PC. The USB FET should be recognized instantly, as the USB device driver should have been installed already with the KickStart software. If for any reason the Install Wizard starts, respond to the prompts and, when prompted, browse to the driver files that are located in <Installation Root>\Embedded Workbench x.x\430\bin\WinXP. Detailed driver installation instructions can be found in Appendix E.

- 2. After connecting to a PC, the USB FET performs a selftest during which the red LED flashes for about 2 seconds. If the selftest passed successfully, the green LED lights permanently.

- 3. Use the 14-conductor cable to connect the USB FET interface module to a target board, such as an MSP-TS430xxx target socket module.

- 4. Ensure that the MSP430 device is securely seated in the socket and that its pin 1 (indicated with a circular indentation on the top surface) aligns with the "1" mark on the PCB.

- 5. Compared to the parallel port debug interface, the USB FET has additional features like: JTAG security fuse blow and adjustable target  $V_{CC}$  (1.8 V to 3.6 V); target can be supplied with up to 100 mA.

# 1.15 Hardware Installation, MSP-eZ430-F2013, MSP-eZ430-RF2500

- 1. Connect the tool to a USB port of your PC.

- The USB FET should be recognized automatically, as the USB device driver should have been installed with the KickStart software. If for any reason the Install Wizard starts, respond to the prompts and, when prompted, browse to the driver files that are located in <Installation Root>\Embedded Workbench x.x\430\bin\WinXP. Detailed driver installation instructions are in Appendix E.

# 1.16 Hardware Installation, MSP-FET430Uxx ('U14, 'U28, 'U38, 'U23x0, 'U48, 'U64, 'U80, 'U100, 'U5x100), MSP-FET430Pxx0 ('P120, 'P140, 'P410, 'P430, 'P440)

- 1. Connect the MSP-FET430PIF or MSP-FET430UIF debug interface to the appropriate port of your PC. Use the 14-conductor cable to connect the FET Interface module to the supplied target socket module.

- 2. Ensure that the MSP430 device is securely seated in the socket, and that its pin 1 (indicated with a circular indentation on the top surface) aligns with the "1" mark on the PCB.

- 3. Ensure that the two jumpers (LED and VCC) near the 2×7-pin male connector are in place. Schematics of the target socket module and its parts are presented in Appendix B.

| Note: Re | legarding 'U38, see FAQ Hardware #2 in Appendix A. |

|----------|----------------------------------------------------|

|----------|----------------------------------------------------|

# 1.17 Flashing the LED

This section demonstrates on the FET the equivalent of the C-language "Hello World!" introductory program. An application that flashes the LED is developed and downloaded to the FET, and then run.

- 1. Start the Workbench (Start → Programs → IAR Systems → IAR Embedded Workbench KickStart for MSP430 V3 → IAR Embedded Workbench).

- 2. Click File → Open Workspace to open the file at: <Installation Root>\Embedded Workbench x.x\430\FET examples\Flashing the LED.eww. The workspace window opens.

- 3. Click on the tab at the bottom of the workspace window that corresponds to your MSP430 device (MSP430xxxx) and desired language (assembler or C).

- 4. Click Project → Options → FET Debugger → Setup → Connection to select the appropriate port: Texas Instruments LPT-IF for the parallel FET Interface (MSP-FET430PIF) or Texas Instruments USB-IF for the USB Interface (MSP-FET430UIF) or for the eZ430.

- 5. Click Project → Rebuild All to build and link the source code. You can view the source code by double-clicking on the project, and then double-clicking on the displayed source file.

- Click Project → Debug to start the C-SPY debugger. C-SPY erases the device flash and then

downloads the application object file to the device flash.

See FAQ Debugging #1 if C-SPY is unable to communicate with the device.

- 7. Click Debug  $\rightarrow$  Go to start the application. The LED should flash.

- 8. Click Debug → Stop Debugging to stop debugging, to exit C-SPY, and to return to the Workbench.

- 9. Click File → Exit to exit the Workbench.

Congratulations, you have just built and tested an MSP430 application!

# 1.18 Important MSP430 Documents on the CD-ROM and Web

The primary sources of MSP430 information are the device-specific data sheet and user's guide. The most up-to-date versions of these documents that are available at the time of production are provided on the CD-ROM included with this tool. The MSP430 web site (<a href="www.ti.com/msp430">www.ti.com/msp430</a>) contains the most recent version of these documents.

PDF documents describing the IAR tools (Workbench/C-SPY, the assembler, the C compiler, the linker, and the librarian) are in the common\doc and 430\doc folders. Supplements to the documents (i.e., the latest information) are available in HTML format in the same directories. 430\doc\readme\_start.htm provides a convenient starting point for navigating the IAR documentation.

# **Development Flow**

This chapter describes how to use KickStart to develop application software and how to use C-SPY to debug it.

| Topic |                 | Page |

|-------|-----------------|------|

| 2.1   | Overview        | 18   |

|       | Using KickStart |      |

| 2.3   | Using C-SPY     | 22   |

Overview www.ti.com

#### 2.1 Overview

Applications are developed in assembler and/or C using the Workbench, and they are debugged using C-SPY. C-SPY is seamlessly integrated into the Workbench. However, it is more convenient to make the distinction between the code development environment (Workbench) and the debugger (C-SPY). C-SPY can be configured to operate with the FET (i.e., an actual MSP430 device), or with a software simulator of the device. KickStart is used to refer to the Workbench and C-SPY collectively. The KickStart software tools are a product of IAR.

Documentation for the MSP430 family and KickStart is extensive. The CD-ROM supplied with this tool contains a large amount of documentation describing the MSP430. The MSP430 home page (<a href="www.ti.com/msp430">www.ti.com/msp430</a>) is another source of MSP430 information. The components of KickStart (workbench/debugger, assembler, compiler, linker) are fully documented in <a href="mailto:lnstallation">lnstallation</a> Root>\Embedded Workbench\430\doc. .htm files located throughout the KickStart directory tree contain the most up-to-date information and supplement the PDF files. In addition, KickStart documentation is available online via Help.

Read Me First files from IAR and TI and this document can be accessed using Start  $\rightarrow$  Programs  $\rightarrow$  IAR Systems  $\rightarrow$  IAR Embedded Workbench KickStart for MSP430 V3.

| Tool                 | User's Guide                 | Most Up-To-Date Information                  |

|----------------------|------------------------------|----------------------------------------------|

| Workbench/C-SPY      | EW430_UsersGuide.pdf         | readme.htm, ew430.htm, cs430.htm, cs430f.htm |

| Assembler            | EW430_AssemblerReference.pdf | a430.htm, a430_msg.htm                       |

| Compiler             | EW430_CompilerReference.pdf  | icc430.htm, icc430_msg.htm                   |

| C library            |                              | CLibrary.htm                                 |

| Linker and Librarian | xlink.pdf                    | xlink.htm, xman.htm, xar.htm                 |

# 2.2 Using KickStart

The KickStart development environment is function limited. The following restrictions are in place:

- The C compiler does not generate an assembly code list file.

- The linker links a maximum of 4K bytes of code originating from C source (but an unlimited amount of code originating from assembler source).

- The simulator inputs a maximum of 4K bytes of code.

A full (i.e., unrestricted) version of the software tools can be purchased from IAR. A mid-featured tool set – called Baseline, with a 12K-byte C-code size limitation and basic floating-point operations – is also available from IAR. Consult the IAR web site (<a href="www.iar.se">www.iar.se</a>) for more information.

# 2.2.1 Project Settings

The settings required to configure the Workbench and C-SPY are numerous and detailed. Please read and thoroughly understand the documentation supplied by IAR when dealing with project settings. Review the project settings of the supplied assembler and C examples (the project settings are accessed using  $Project \rightarrow Options$  with the project name selected). Use these project settings as templates when developing your own projects. Note that if the project name is not selected when settings are made, the settings are applied to the selected file (not to the project).

The following project settings are recommended/required:

- Specify the target device (General Options → Target → Device).

- Enable an assembler project or a C/assembler project (General Options → Target → Assembler-only project).

- Enable the generation of an executable output file (General Options → Output → Output file →

Executable).

- To most easily debug a C project, disable optimization [C/C++ Compiler → Optimizations → Size → None (Best debug support)].

www.ti.com Using KickStart

- Enable the generation of debug information in the compiler output (C/C++ Compiler → Output →

Generate debug information).

- Specify the search path for the C preprocessor (C/C++ Compiler → Preprocessor → Include Paths).

- Enable the generation of debug information in the assembler output (Assembler → Output → Generate Debug Info).

- Specify the search path for the assembler preprocessor (Assembler → Preprocessor → Include Paths).

- To debug the project using C-SPY, specify a compatible format [Linker → Output → Format → Debug information for C-SPY (With runtime control modules/With I/O emulation modules)].

- Specify the search path for any used libraries (Linker → Config → Search paths).

- Specify the C-SPY driver. Select Project → Options → Debugger → Setup → Driver → FET Debugger to debug on the FET (i.e., MSP430 device). Select Simulator to debug on the simulator. If FET Debugger is selected, use Project → Options → FET Debugger → Setup → Connection to select the appropriate port: Texas Instruments LPT-IF for the parallel FET Interface (MSP-FET430PIF) or Texas Instruments USB-IF for the USB Interface (MSP-FET430UIF) or for the eZ430.

- Enable the Device Description file. This file makes C-SPY "aware" of the specifics of the device it is debugging. This file corresponds to the specified target device (Debugger → Setup → Device description file → Override default).

- Enable the erasure of the Main and Information memories before object code download (FET Debugger → Download → Erase main and Information memory).

- To maximize system performance during debug, disable Virtual Breakpoints (FET Debugger →

Breakpoints → Use virtual breakpoints) and disable all System Breakpoints (FET Debugger →

Breakpoints → System breakpoints on).

#### Note: Use Factory Settings to quickly configure a project.

Use the Factory Settings button to quickly configure a project to a usable state.

The following steps can be used to quickly configure a project. Note that the General Options tab does not have a Factory Settings button.

- 1. Specify the target device (General Options  $\rightarrow$  Target  $\rightarrow$  Device).

- 2. Enable an assembler project or a C/assembler project (General Options → Target → Assembler-only project).

- Enable the generation of an executable output file (General Options → Output → Output file →

Executable).

- 4. Accept the factory settings for the compiler (C/C++ Compiler → Factory Settings).

- 5. Accept the factory settings for the assembler (Assembler → Factory Settings).

- 6. Accept the factory settings for the linker (Linker → Factory Settings).

- 7. Accept the factory settings for C-SPY (Debugger → Factory Settings).

- 8. Debug on the hardware (Debugger  $\rightarrow$  Setup  $\rightarrow$  Driver  $\rightarrow$  FET Debugger).

- Specify the active parallel port used to interface to the FET if not LPT1 (FET Debugger → Setup →

Connection → Texas Instruments LPT-IF) or specify the USB port (FET Debugger → Setup →

Connection → Texas Instruments USB-IF).

#### Note: Avoid the use of absolute path names when referencing files.

Instead, use the relative pathname keywords \$TOOLKIT\_DIR\$ and \$PROJ\_DIR\$. See the IAR documentation for a description of these keywords. The use of relative path names permits projects to be moved easily, and projects do not require modification when IAR systems are upgraded (e.g., from KickStart or Baseline to Full).

Using KickStart www.ti.com

# 2.2.2 Creating a Project From Scratch

This section presents step-by-step instructions to create an assembler or C project from scratch, and to download and run the application on the MSP430 (see also Section 2.2.1, Project Settings). The MSP430 IAR Embedded Workbench IDE User's Guide presents a more comprehensive overview of the process.

- Start the Workbench (Start → Programs → IAR Systems → IAR Embedded Workbench KickStart for MSP430 V3 → IAR Embedded Workbench).

- 2. Create a new text file (File  $\rightarrow$  New  $\rightarrow$  File).

- 3. Enter the program text into the file.

#### Note: Use .h files to simplify your code development.

KickStart is supplied with files that define the device registers and the bit names for each device. These files can greatly simplify the task of developing your program. The files are located in <Installation Root>\Embedded Workbench x.x\430\inc. Include the .h file corresponding to your target device in your text file (#include "msp430xyyy.h"). Additionally, files io430xxxx.h are provided and are optimized to be included by C source files.

- 4. Save the program text file (File  $\rightarrow$  Save).

- It is recommended that assembler text files be saved with a file-type suffix of ".s43" and that C text files be saved with a file-type suffix of ".c".

- 5. Create a new workspace (File  $\rightarrow$  New  $\rightarrow$  Workspace).

- 6. Create a new project (Project → Create New Project). Select Tool chain: MSP430, Project Templates: Empty project and click OK. Specify a project name and click Save.

- 7. Add the program text file to the project (Project → Add Files). Select the program text file and click Open. Alternatively, double-click on the file to add it to the project.

#### Note: How to add assembler source files to your project

The default file type presented in the Add Files window is "C/C++ Files". To view assembler files (.s43), select "Assembler Files" in the "Files of type" drop-down menu.

- 8. Save the workspace (File  $\rightarrow$  Save Workspace). Specify a workspace name and click Save.

- Configure the project options (Project → Options). For each of the subcategories (General Options, C/C++ Compiler, Assembler, Linker, Debugger), accept the default Factory Settings with the following exceptions:

- Specify the target device (General Options → Target → Device).

- Enable an assembler project or a C/assembler project (General Options → Target →

Assembler-only project).

- Enable the generation of an executable output file (General Options → Output → Output file →

Executable).

- To debug on the FET (i.e., the MSP430), click Debugger → Setup → Driver → FET Debugger.

- Specify the active port used to interface to the FET (FET Debugger → Setup → Connection).

- 10. Build the project (Project → Rebuild All).

- 11. Debug the application using C-SPY (Project → Debug). This starts C-SPY, and C-SPY takes control of the target, erases the target memory, programs the target memory with the application, and resets the target.

- See FAQ Debugging #1 if C-SPY is unable to communicate with the device.

- 12. Click Debug  $\rightarrow$  Go to start the application.

- 13. Click Debug  $\rightarrow$  Stop Debugging to stop the application, to exit C-SPY, and to return to the Workbench.

- 14. Click File → Exit to exit the Workbench.

www.ti.com Using KickStart

# 2.2.3 Using an Existing IAR V1.x/V2.x/V3.x Project

It is possible to use an existing project from an IAR V1.x/V2.x/V3.x system with the new IAR V4.x system; see the IAR document *Step by Step Migration for EW430 x.xx*. This document is in <Installation Root>\Embedded Workbench x.x\430\doc\migration.htm.

# 2.2.4 Stack Management and .xcl Files

The reserved stack size can be configured through either the project options dialog (General Options  $\rightarrow$  Stack/Heap) or through direct modification of the .xcl linker control files. These files are input to the linker and contain statements that control the allocation of device memory (RAM, flash). See the IAR XLINK documentation for a complete description of these files. The .xcl files provided with the FET (<Installation Root>\Embedded Workbench x.x\430\config\lnk430xxxx.xcl) define a relocatable segment (RSEG) called CSTACK. CSTACK is used to define the region of RAM that is used for the system stack within C programs. CSTACK can also be used in assembler programs (MOV.W #SFE(CSTACK), SP). CSTACK is defined to extend from the last location of RAM for 50 bytes (i.e., the stack extends downward through RAM for 50 bytes).

Other statements in the .xcl file define other relocatable regions that are allocated from the first location of RAM to the bottom of the stack. It is critical to note that:

- The supplied .xcl files reserve 50 bytes of RAM for the stack, regardless if this amount of stack is actually required (or if it is sufficient).

- There is no runtime checking of the stack. The stack can overflow the 50 reserved bytes and possibly overwrite the other segments. No error is output.

The supplied .xcl files can be modified to tune the size of the stack to the needs of the application; edit -D\_STACK\_SIZE=xx to allocate xx bytes for the stack. Note that the .xcl file also reserves 50 byes for the heap if required (for example, by malloc()).

# 2.2.5 How to Generate Texas Instruments .TXT (and Other Format) Files

The KickStart linker can be configured to output objects in TI .TXT format for use with the GANG430 and PRGS430 programmers. Click Project  $\rightarrow$  Options  $\rightarrow$  Linker  $\rightarrow$  Output  $\rightarrow$  Format  $\rightarrow$  Other  $\rightarrow$  msp430-txt. Intel<sup>TM</sup> and Motorola<sup>TM</sup> formats also can be selected.

For more information, see FAQ Program Development #6 in Appendix A.

# 2.2.6 Overview of Example Programs

Example programs for MSP430 devices are provided in <Installation Root>\Embedded Workbench x.x\430\FET\_examples. Each tool folder contains folders that contain the assembler and C sources.

<Installation Root>\Embedded Workbench\x.x\430\FET\_examples\Flashing the LED.eww conveniently organizes the FET\_1 demonstration code into a workspace. The workspace contains assembler and C projects of the code for each of the MSP430 device families. Debug and Release versions are provided for each of the projects.

<Installation Root>\Embedded Workbench x.x\430\FET\_examples\contents.htm conveniently organizes and documents the examples.

Additional code examples can be found on the MSP430 home page under Code Examples.

**Note:** Some example programs require a 32-kHz crystal on LFXT1, and not all FETs are supplied with a 32-kHz crystal.

Using C-SPY www.ti.com

# 2.3 Using C-SPY

See Appendix C for a description of FET-specific menus within C-SPY.

# 2.3.1 Breakpoint Types

The C-SPY breakpoint mechanism uses a limited number of on-chip debugging resources (specifically, N breakpoint registers, see Table 2-1). When N or fewer breakpoints are set, the application runs at full device speed (or realtime). When greater than N breakpoints are set and Use Virtual Breakpoints is enabled (FET Debugger → Breakpoints → Use virtual breakpoints), the application runs under the control of the host PC; the system operates at a much slower speed but offers unlimited software breakpoints (or non-realtime). During non-realtime mode, the PC, in effect, repeatedly single steps the device and interrogates the device after each operation to determine if a breakpoint has been hit.

Both (code) address and data (value) breakpoints are supported. Data breakpoints and range breakpoints each require two MSP430 hardware breakpoints.

Table 2-1. Number of Device Breakpoints and Other Emulation Features

| Device       | 4-Wire<br>JTAG | 2-Wire<br>Spy-Bi-Wire | Breakpoints<br>(N) | Range<br>Breakpoints | Clock<br>Control | State<br>Sequencer | Trace<br>Buffer |

|--------------|----------------|-----------------------|--------------------|----------------------|------------------|--------------------|-----------------|

| MSP430F11x1  | Х              | -17                   | 2                  |                      |                  |                    |                 |

| MSP430F11x2  | Х              |                       | 2                  |                      |                  |                    |                 |

| MSP430F12x   | Х              |                       | 2                  |                      |                  |                    |                 |

| MSP430F12x2  | Х              |                       | 2                  |                      |                  |                    |                 |

| MSP430F13x   | Х              |                       | 3                  | Х                    |                  |                    |                 |

| MSP430F14x   | Χ              |                       | 3                  | Х                    |                  |                    |                 |

| MSP430F15x   | Χ              |                       | 8                  | X                    | Χ                | X                  | Х               |

| MSP430F16x   | Χ              |                       | 8                  | Х                    | Χ                | Х                  | Х               |

| MSP430F161x  | Χ              |                       | 8                  | Х                    | Х                | Х                  | Х               |

| MSP430F20xx  | Х              | Х                     | 2                  |                      | Х                |                    |                 |

| MSP430F21x1  | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430F21x2  | Х              | X                     | 2                  |                      | Х                |                    |                 |

| MSP430F22x2  | Х              | Х                     | 2                  |                      | Х                |                    |                 |

| MSP430F22x4  | Х              | Х                     | 2                  |                      | Х                |                    |                 |

| MSP430F23x   | Х              |                       | 3                  | Х                    | Х                |                    |                 |

| MSP430F23x0  | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430F24x   | Х              |                       | 3                  | Х                    | Х                |                    |                 |

| MSP430F24x1  | Х              |                       | 3                  | Х                    | Х                |                    |                 |

| MSP430F2410  | Х              |                       | 3                  | Х                    | Х                |                    |                 |

| MSP430F241x  | Х              |                       | 8                  | Х                    | Х                | Х                  | Х               |

| MSP430F261x  | Х              |                       | 8                  | Х                    | Х                | Х                  | Х               |

| MSP430F41x   | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430F42x   | Χ              |                       | 2                  |                      | Х                |                    |                 |

| MSP430FE42x  | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430FE42x2 | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430FW42x  | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430F42x0  | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430FG42x0 | Χ              |                       | 2                  |                      | Х                |                    |                 |

| MSP430F43x   | Х              |                       | 8                  | X                    | Х                | X                  | Х               |

| MSP430FG43x  | Χ              |                       | 2                  |                      | Х                |                    |                 |

| MSP430F43x1  | Χ              |                       | 8                  | X                    | Х                | X                  | Х               |

| MSP430F44x   | Χ              |                       | 8                  | X                    | Χ                | X                  | Х               |

| MSP430FG461x | Х              |                       | 8                  | X                    | Х                | Х                  | Х               |

Using C-SPY www.ti.com

8

|             |                |                       | •                  |                      |                  | •                  | ,               |

|-------------|----------------|-----------------------|--------------------|----------------------|------------------|--------------------|-----------------|

| Device      | 4-Wire<br>JTAG | 2-Wire<br>Spy-Bi-Wire | Breakpoints<br>(N) | Range<br>Breakpoints | Clock<br>Control | State<br>Sequencer | Trace<br>Buffer |

| MSP430F47x3 | Х              |                       | 2                  |                      | Х                |                    |                 |

| MSP430F47x4 | Х              |                       | 2                  |                      | Х                |                    |                 |

Χ

Χ

Χ

Х

Table 2-1. Number of Device Breakpoints and Other Emulation Features (continued)

# 2.3.2 Using Breakpoints

MSP430F54xx

Χ

Χ

If C-SPY is started with greater than N breakpoints set and virtual breakpoints are disabled, a message is output to inform the user that only N (realtime) breakpoints are enabled (and one or more breakpoints are disabled). Note that the workbench permits any number of breakpoints to be set, regardless of the Use Virtual Breakpoints setting of C-SPY. If virtual breakpoints are disabled, a maximum of N breakpoints can be set within C-SPY.

Resetting a program temporarily requires a breakpoint if Project  $\rightarrow$  Options  $\rightarrow$  Debugger  $\rightarrow$  Setup  $\rightarrow$ Run To is enabled (see FAQ Debugging #32).

The Run To Cursor operation temporarily requires a breakpoint. Consequently, only N – 1 breakpoints can be active when Run To Cursor is used if virtual breakpoints are disabled (see FAQ Debugging #33).

If, while processing a breakpoint, an interrupt becomes active, C-SPY stops at the first instruction of the interrupt service routine (see FAQ Debugging #26).

# 2.3.3 Using Single Step

When debugging an assembler file, Step Over, Step Out, and Next Statement operate like Step Into; i.e., the current instruction is executed at full speed.

When debugging an assembler file, a step operation of a CALL instruction stops at the first instruction of the called function.

When debugging an assembler file, a (true) Step Over a CALL instruction that executes the called function at full device speed can be synthesized by placing a breakpoint after the CALL and using GO (to the breakpoint in realtime mode).

When debugging a C file, a single step (Step) operation executes the next C statement. Thus, it is possible to step over a function reference. If possible, a hardware breakpoint is placed after the function reference, and a GO is implicitly executed. This causes the function to be executed at full speed. If no hardware breakpoints are available, the function is executed in non-realtime mode. Step Into is supported. Step Out is supported.

Within Disassembly mode (View  $\rightarrow$  Disassembly), a step operation of a non-CALL instruction executes the instruction at full device speed.

Within Disassembly mode (View → Disassembly), a step operation of a CALL instruction places, if possible, a hardware breakpoint after the CALL instruction, and then executes Go. The called function executes at full device speed. If no hardware breakpoint is available prior to the Go, the called function is executed in non-realtime mode. In either case, execution stops at the instruction following the CALL.

It is possible to single step only when source statements are present. Breakpoints must be used when running code for which there is no source code (i.e., place the breakpoint after the CALL to the function for which there is no source, and then Go to the breakpoint in realtime mode).

If, during a single step operation, an interrupt becomes active, the current instruction is completed and C-SPY stops at the first instruction of the interrupt service routine (see FAQ Debugging #26).

Using C-SPY www.ti.com

# 2.3.4 Using Watch Windows

The C-SPY Watch Window mechanism permits C variables to be monitored during the debugging session. Although not originally designed to do so, the Watch Window mechanism can be extended to monitor assembler variables.

Assume that the variables to watch are defined in RAM, for example:

```

RSEG DATA16_I

varword ds 2; two bytes per word

varchar ds 1; one byte per character

```

#### In C-SPY:

- 1. Open the Watch Window (View → Watch).

- 2. Click Debug → Quick Watch.

- 3. To watch varword, enter in the Expression box:

(\_\_data16 unsigned int \*) varword

- 4. To watch varchar, enter in the Expression box: (\_\_data16 unsigned char \*) varchar

- 5. Click the Add Watch button.

- 6. Close the Quick Watch window.

- 7. For the created entry in the Watch Window, click on the + symbol to display the contents (or value) of the watched variable.

To change the format of the displayed variable (default, binary, octal, decimal, hex, char), select the type, click the right mouse button, and then select the desired format. The value of the displayed variable can be changed by selecting it, and then entering the new value.

In C, variables can be watched by selecting them and then dragging and dropping them into the Watch Window.

Because the MSP430 peripherals are memory mapped, it is possible to extend the concept of watching variables to watching peripherals. Be aware that there may be side effects when peripherals are read and written by C-SPY (see FAQ Debugging #24).

CPU core registers can be specified for watching by preceding their name with '#' (i.e., #PC, #SR, #SP, #R5, etc.).

Variables watched within the Watch Window are updated only when C-SPY gets control of the device (for example, following a breakpoint hit, a single step, or a stop/escape).

Although registers can be monitored in the Watch Window, View  $\rightarrow$  Register is the preferred method.

# Design Considerations for In-Circuit Programming

This chapter presents signal requirements for in-circuit programming of the MSP430.

| Topic |                                                                                                            | Page |

|-------|------------------------------------------------------------------------------------------------------------|------|

| 3.1   | Signal Connections for In-System Programming and Debugging, MSP-FET430PIF, MSP-FET430UIF, GANG430, PRGS430 | 26   |

| 3.2   | External Power                                                                                             | 29   |

| 3.3   | Bootstrap Loader                                                                                           | 29   |

# 3.1 Signal Connections for In-System Programming and Debugging, MSP-FET430PIF, MSP-FET430UIF, GANG430, PRGS430

With the proper connections, the C-SPY debugger and an FET hardware JTAG interface, such as the MSP-FET430PIF and MSP-FET430UIF, can be used to program and debug code on a target board. In addition, the connections can also support the GANG430 or PRGS430 production programmers, which provide an easy way to program prototype boards, if desired.

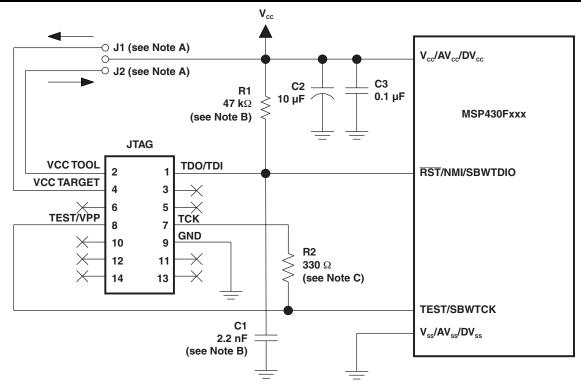

Figure 3-1 shows the connections between the 14-pin FET Interface module connector and the target device required to support in-system programming and debugging using C-SPY for 4-wire JTAG communication. Figure 3-2 shows the connections for 2-wire Spy-Bi-Wire communication. While 4-wire JTAG mode is generally supported on all MSP430 devices, 2-wire Spy-Bi-Wire mode is available on selected devices only. See Table 2-1 for information on which interfacing method can be used on which device.

The connections for the FET Interface module and the GANG430 or PRGS430 are identical. Both the FET interface module and GANG430 can supply  $V_{CC}$  to your target board (via pin 2). In addition, the FET interface module and GANG430 have a  $V_{CC}$ -sense feature that, if used, requires an alternate connection (pin 4 instead of pin 2). The  $V_{CC}$ -sense feature senses the local  $V_{CC}$  (present on the target board, i.e., a battery or other local power supply) and adjusts the output signals accordingly. If the target board is to be powered by a local  $V_{CC}$ , the connection to pin 4 on the JTAG should be made and not the connection to pin 2. This utilizes the  $V_{CC}$ -sense feature and prevents any contention that might occur if the local on-board  $V_{CC}$  were connected to the  $V_{CC}$  supplied from the FET interface module or the GANG430. If the  $V_{CC}$ -sense feature is not necessary (i.e., the target board is to be powered from the FET Interface module or the GANG430) the  $V_{CC}$  connection is made to pin 2 on the JTAG header and no connection is made to pin 4. Figure 3-1 and Figure 3-2 show a jumper block that supports both scenarios of supplying  $V_{CC}$  to the target board. If this flexibility is not required, the desired  $V_{CC}$  connections may be hard-wired, eliminating the jumper block. Pins 2 and 4 must not be connected simultaneously.

Note that in 4-wire JTAG communication mode (see Figure 3-1), the connection of the target RST signal to the JTAG connector is optional when using 4-wire JTAG communication mode capable only devices. However, when using 2-wire Spy-Bi-Wire communication mode capable devices in 4-wire JTAG mode, the RST connection must be made. The MSP430 development tools and device programmers perform a target reset by issuing a JTAG command to gain control over the device. However, if this is unsuccessful, the RST signal of the JTAG connector can be used by the development tool or device programmer as an additional way to assert a device reset.

V<sub>cc</sub> J1 (see Note A) V<sub>cc</sub>/AV<sub>cc</sub>/DV<sub>cc</sub> J2 (see Note A) C3 C2 R1 0.1 µF 10 μF 47  $\mathbf{k}\Omega$ MSP430Fxxx (see Note B) **JTAG** RST/NMI **VCC TOOL** TDO/TDI TDO/TDI **VCC TARGET** TDI/VPP TDI/VPP 4 3 **TMS** 5 **TMS** TEST/VPP **TCK** 7 **TCK GND** 10 9 RST (see Note D) 11 12 14 13 TEST/VPP (see Note C) C<sub>1</sub> 10 nF/2.2 nF V<sub>ss</sub>/AV<sub>ss</sub>/DV<sub>ss</sub> (see Notes B and E)

- A Make either connection J1 (if a local target power supply is used) or connection J2 (if powering the from the debug/programming adapter).

- B The RST/NMI pin R1/C1 configuration is device-family dependent. See the respective MSP430 family user's guide for the recommended configuration.

- C The TEST/VPP pin is available only on MSP430 family members with multiplexed JTAG pins. See the device data sheet to determine if this pin is available.

- D The connection to the JTAG connector RST pin is optional when using 4-wire JTAG communication mode capable-only devices and is not required for device programming or debugging. However, this connection is required when using 2-wire Spy-Bi-Wire communication mode capable devices in 4-wire JTAG mode.

- E When using 2-wire Spy-Bi-Wire communication capable devices in 4-wire JTAG mode, the upper limit for C1 should not exceed 2.2 nF. This applies to both TI FET interface modules (LPT/USB FET).

Figure 3-1. Signal Connections for 4-Wire JTAG Communication

- A Make either connection J1 (if a local target power supply is used) or connection J2 (if powering the from the debug/programming adapter).

- B The device RST/NMI/SBWTDIO pin is used in 2-wire Spy-Bi-Wire mode for bidirectional debug communication with the device and that any capacitance attached to this signal may affect the ability to establish a connection with the device. The upper limit for C1 is 2.2 nF when using current TI FET Interface modules (USB FET).

- C R2 is used to protect the JTAG debug interface TCK signal against the JTAG security fuse blow voltage that is supplied by the TEST/VPP pin during the fuse blow process. In the case that fuse blow functionality is not needed, R2 is not required (becomes  $0~\Omega$ ), and the connection TEST/VPP must not be made.

Figure 3-2. Signal Connections for 2-Wire Spy-Bi-Wire Communication

www.ti.com External Power

#### 3.2 External Power

The PC parallel port can source only a limited amount of current. Because of the ultralow-power capability of the MSP430, a standalone FET does not exceed the available current. However, if additional circuitry is added to the tool, this current limit could be exceeded. In this case, external power can be supplied to the tool via connections provided on the MSP-FET430X110 and the target socket modules. See the schematics of the MSP-FET430X110 and the target socket modules in Appendix B to locate the external power connectors.

The MSP-FET430UIF can supply targets with up to 100 mA through pin 2 of the 14-pin connector.  $V_{CC}$  for the target can be selected between 1.8 V and 3.6 V in steps of 0.1 V. Alternatively, the target can be supplied externally. In this case, the external voltage should be connected to pin 4 of the 14-pin connector. The MSP-FET430UIF then automatically adjusts the level of the JTAG signals to external  $V_{CC}$ . Only pin 2 (if MSP-FET430UIF supplies target) or pin 4 (if target is externally supplied) must be connected, not both at the same time.

When an MSP-FET430X110 is powered from an external supply, an on-board device regulates the external voltage to the level required by the MSP430.

When a target socket module is powered from an external supply, the external supply powers the device on the target socket module and any user circuitry connected to the target socket module, and the FET interface module continues to be powered from the PC via the parallel port. If the externally supplied voltage differs from that of the FET interface module, the target socket module must be modified so that the externally supplied voltage is routed to the FET interface module (so that it may adjust its output voltage levels accordingly). See the target socket module schematics in Appendix B.

# 3.3 Bootstrap Loader

The JTAG pins provide access to the flash memory of the MSP430Fxxx devices. On some devices, these pins are shared with the device port pins, and this sharing of pins can complicate a design (or it may simply not be possible to do so). As an alternative to using the JTAG pins, most MSP430Fxxx devices contain a program (a "Bootstrap Loader") that permits the flash memory to be erased and programmed simply, using a reduced set of signals. Application reports <a href="SLAA089">SLAA089</a> and <a href="SLAA096">SLAA096</a> fully describe this interface. TI does not produce a BSL tool. However, customers can easily develop their own BSL tools using the information in the application reports, or BSL tools can be purchased from third parties. See the MSP430 web site for the application reports and a list of MSP430 third-party tool developers.

TI suggests that MSP430Fxxx customers design their circuits with the BSL in mind (i.e., TI suggests providing access to these signals via, for example, a header).

See FAQ Hardware #11 for a second alternative to sharing the JTAG and port pins.

The BSL tool requires the following device signals:

- RST/NMI

- TEST<sup>(1)</sup> or TCK

- GND

- VCC

- P1.1

- P2.2 or P1.0<sup>(2)</sup>

- (1) If present on device

- $^{(2)}$  '1xx and '2xx devices use pins P1.1 and P2.2 for the BSL. '4xx devices use pins P1.0 and P1.1 for the BSL.

# Frequently Asked Questions

This appendix presents solutions to frequently asked questions regarding hardware, program development, and debugging tools.

| То | pic  |                                                     | Page |

|----|------|-----------------------------------------------------|------|

|    | ۸ 1  | Hardware                                            | 5    |

|    | Α. Ι | natuwate                                            | 32   |

|    | A.2  | Program Development (Assembler, C-Compiler, Linker) | 33   |

|    | A.3  | Debugging (C-SPY)                                   | 35   |

Hardware www.ti.com

#### A.1 Hardware

1. The state of the device (CPU registers, RAM memory, etc.) is undefined following a reset. Exceptions to the above statement are that the PC is loaded with the word at 0xFFFE (i.e., the reset vector), the status register is cleared, and the peripheral registers (SFRs) are initialized as documented in the device-family user's guides. C-SPY resets the device after programming it.

- 2. MSP430F22xx Target Socket Module (MSP-TS430DA38) Important Information Due to the large capacitive coupling introduced by the device socket between the adjacent signals XIN/P2.6 (socket pin 6) and RST/SBWTDIO (socket pin 7), in-system debugging can disturb the LFXT1 low-frequency crystal oscillator operation (ACLK). This behavior applies only to the Spy-Bi-Wire (2-wire) JTAG configuration and only to the period while a debug session is active. Workarounds: